写在前面:

因笔者为初学者,所以在阅读本笔记之前你要有本文会出现以下致命错误的心理准备:概念解释错误、操作错误、专业术语使用错误等低级错误

但笔者会秉承着对信息的尊重,尽可能的减少上述错误以增大本文的可参考性和可学习性

以上,共勉

1.1 安装Quartus

先下载官网的版本

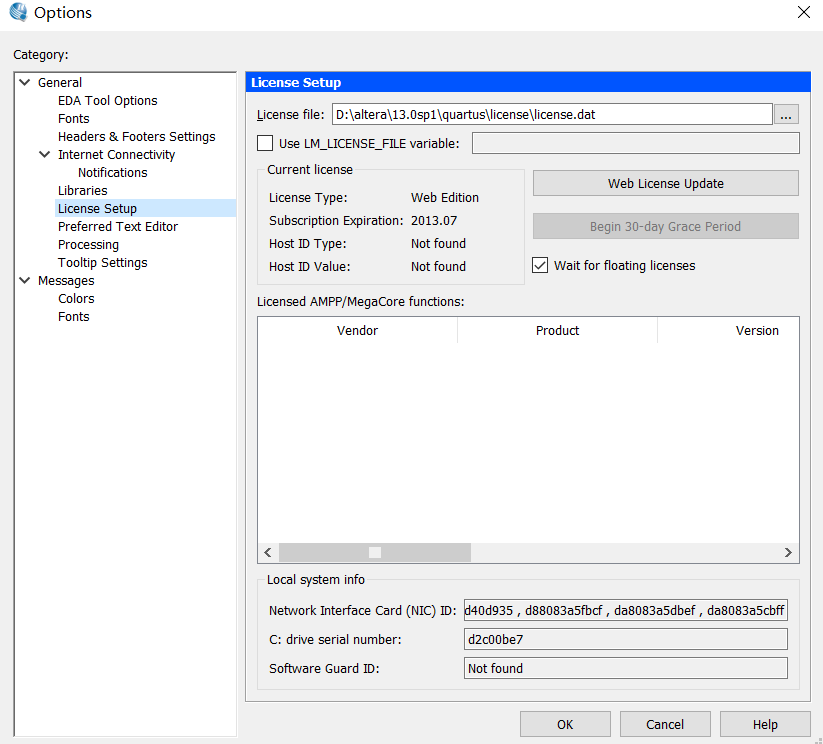

然后用网上的破解器选择dll文件,进行生成许可证操作,生成完的许可证里的XXXXXX要用tools/license setup里的NIC(ID)替换,然后选择这个许可证文件即可

2.1 Quartus的Hello World

接着创建新项目测试软件的可用性:

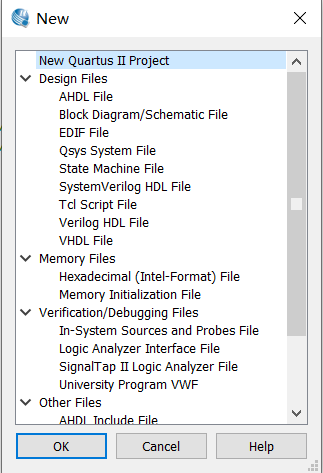

点击左上角的 File / New:

点击New Quartus || Project,随后依据引导进行创建即可

接着还是点击 New ,这次创建Design Files / Verilog HDL File,复制以下代码:

1 | // 文件名:main.v |

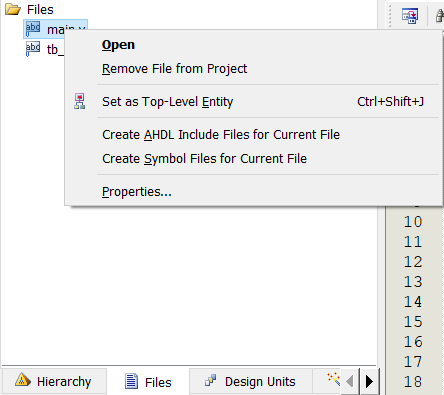

接着在Files侧边栏里将这个文件设置为顶层文件

然后按照同样的步骤创建一个测试文件tb_main.v,内容为:

1 | // 文件名:tb_main.v |

这个文件不用设置成顶层文件

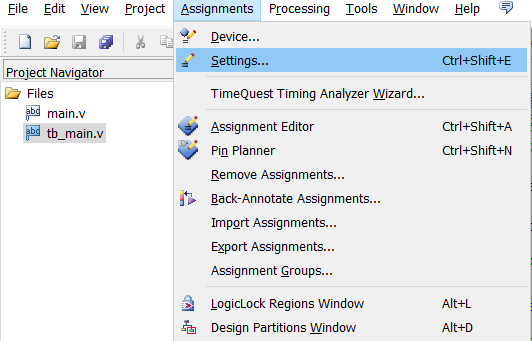

然后配置模拟器,点击Assignments / Settings:

点击EDA Tool Settings / Simulation, 选择Tool name为ModelSim-Altera, 选择Format for output netlist为Verilog HDL

然后点击Project / Add/Remove Files in Project将tb_main.v添加进去

接着就可以点击Tools / Run Simulation Tool / RTL Simulation进行模拟了

能正常运行就说明软件可以正常工作,可以进行下一步了

3.1 画第一个全加器电路图

很好,准备工作已经全部完成了,接下来我们创建第一个真正的项目吧~

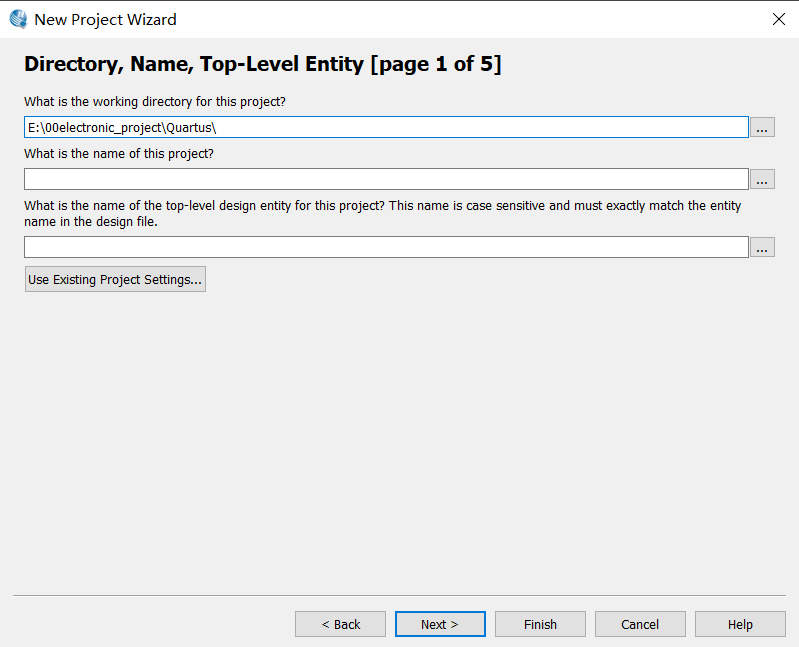

首先按照 2.1 Quartus的Hello World 的方法点开创建项目的对话框:

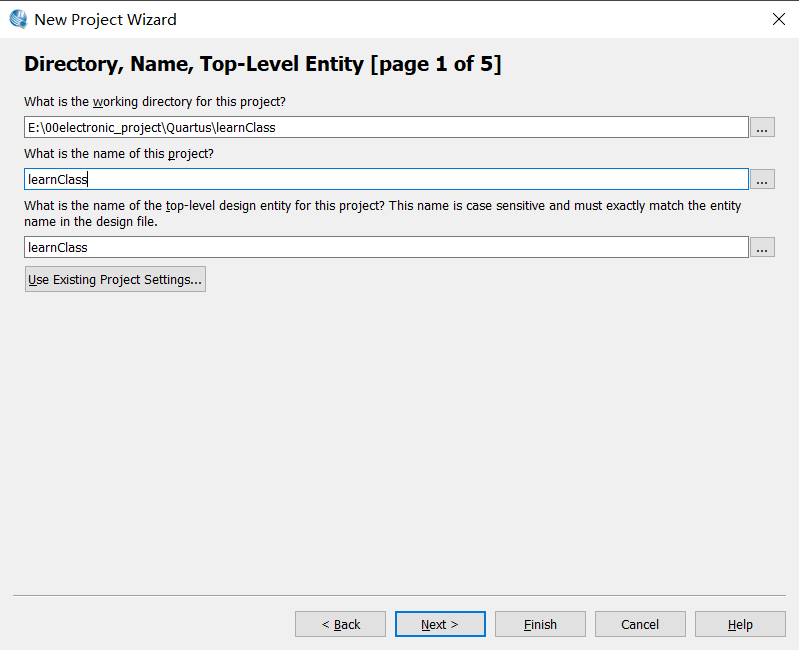

按照以下截图的配置进行创建,注意项目路径:存放在一个方便查找的位置,填好项目名后最好在存放路径后面手动添加同名的目录名,因为Quartus不会自动为项目创建一个新目录,所以最好指定一个空的目录存放项目文件,然后复制这个项目路径

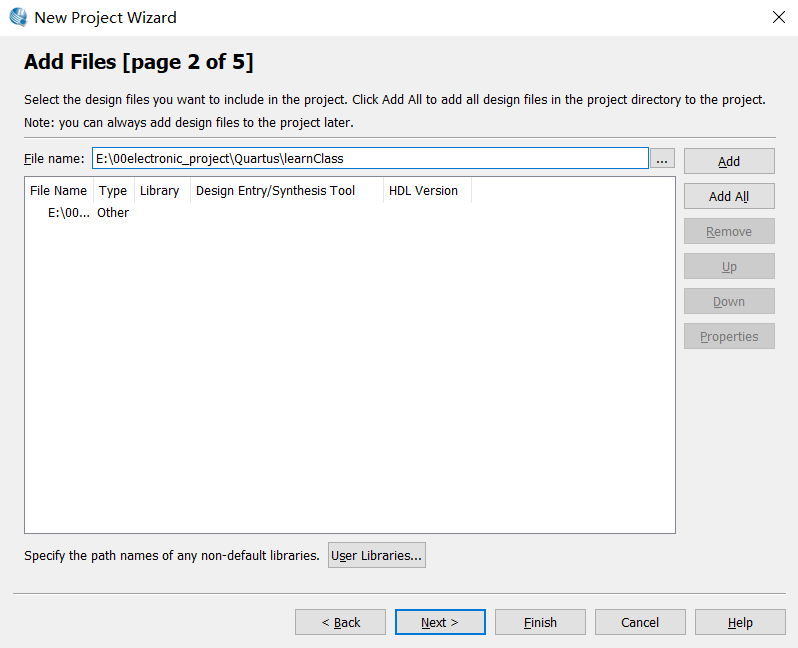

把刚刚的复制的路径Add进Files里面

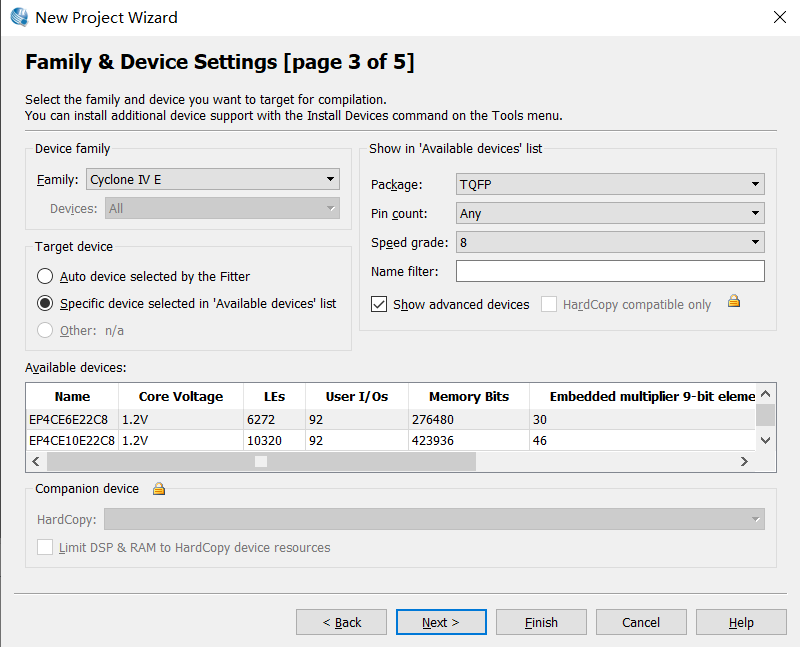

设备参数按照如下设置进行配置

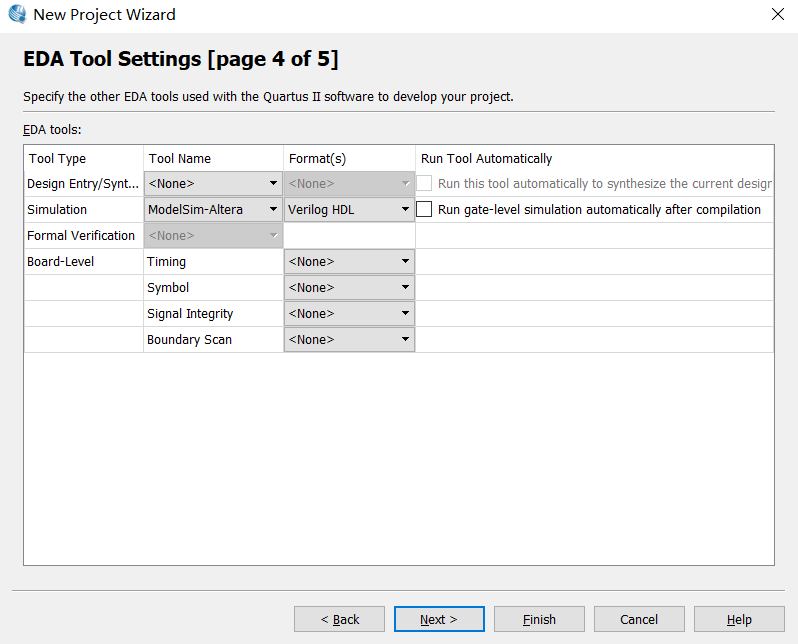

EDA工具设置

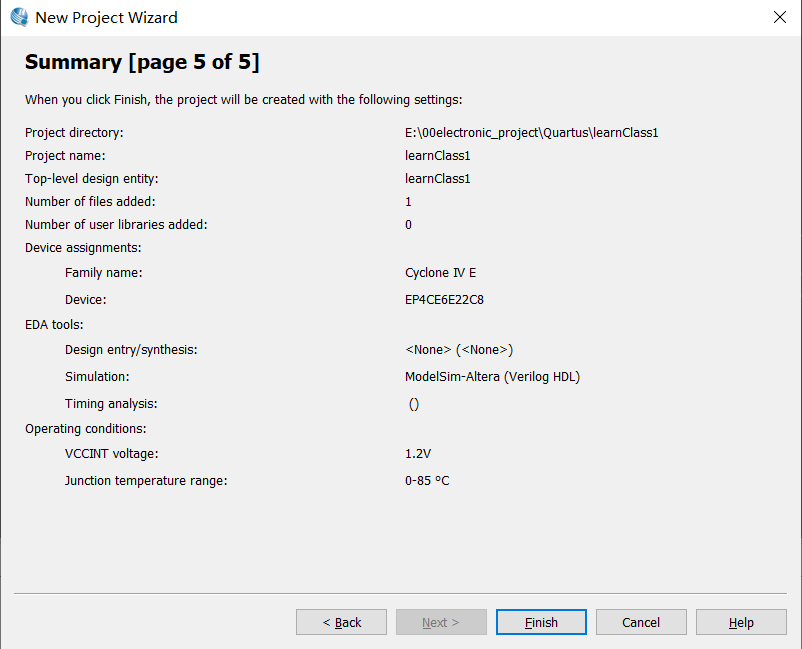

最后Next

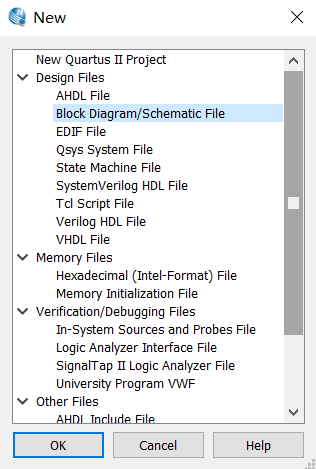

然后创建一个Block Diagram/Schematic File

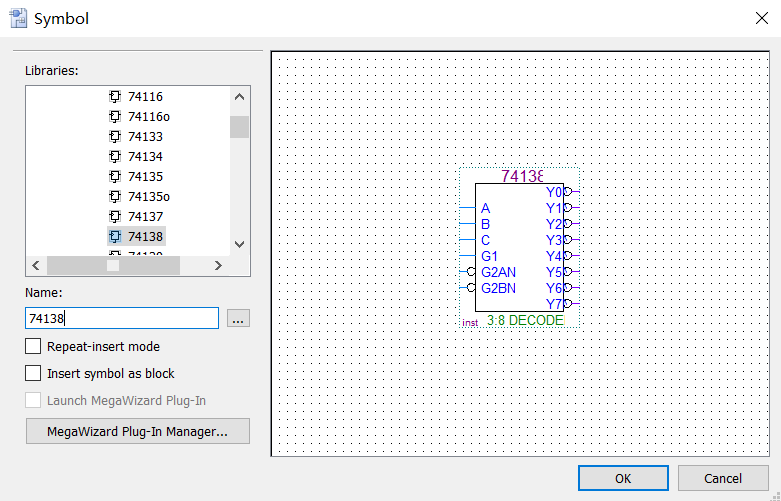

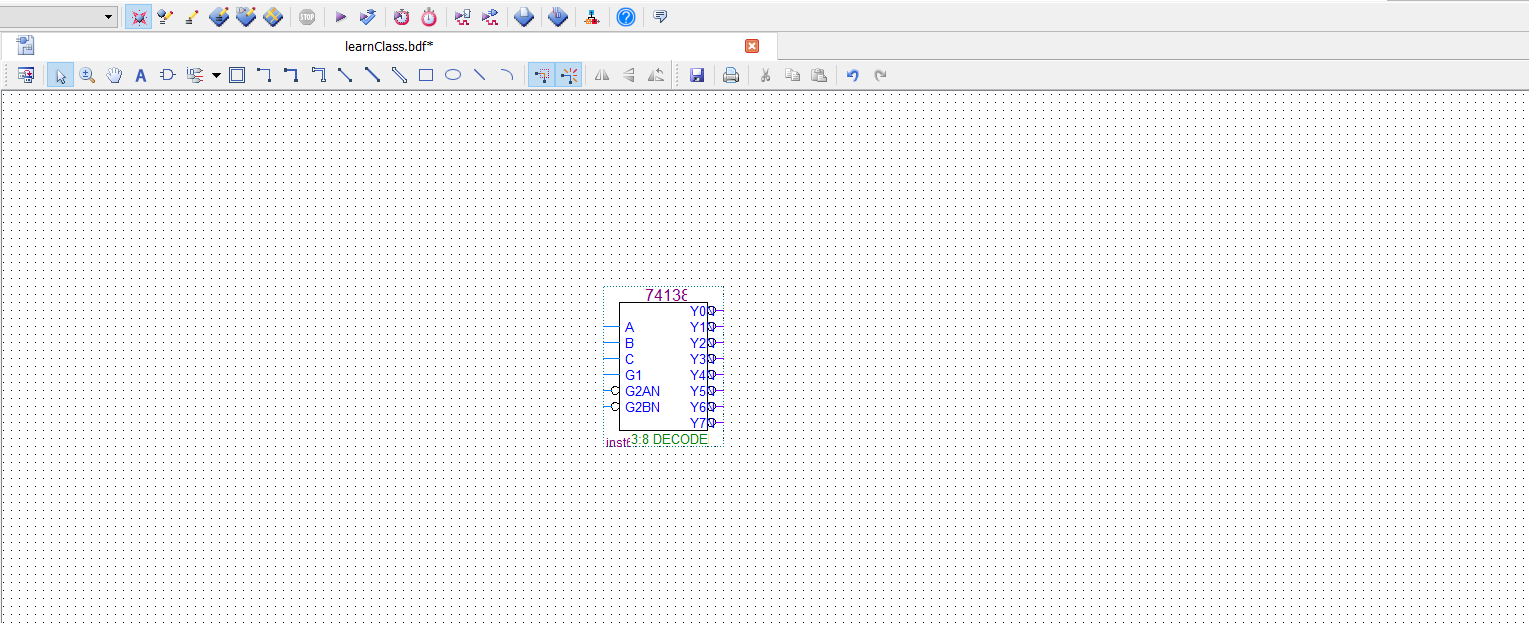

双击空白画布打开对话框输入74138点击ok添加初始开发板:

接着点击画布任意处放置该开发板

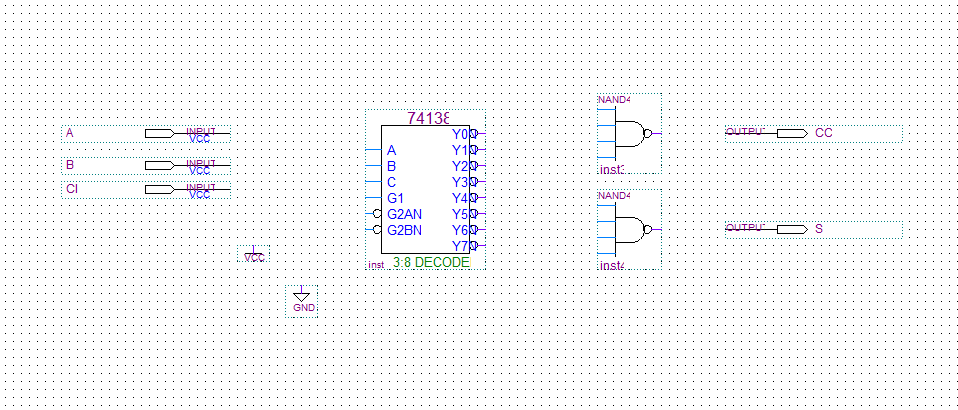

接着按照同样的方法添加三个INPUT(分别命名为A、B和C)、两个NAND4、两个OUTPUT(分别命名为CC和S)以及VCC和GND,其中VCC需要对其右键点击Flip Vertical将其垂直翻转使得接线口位于上方

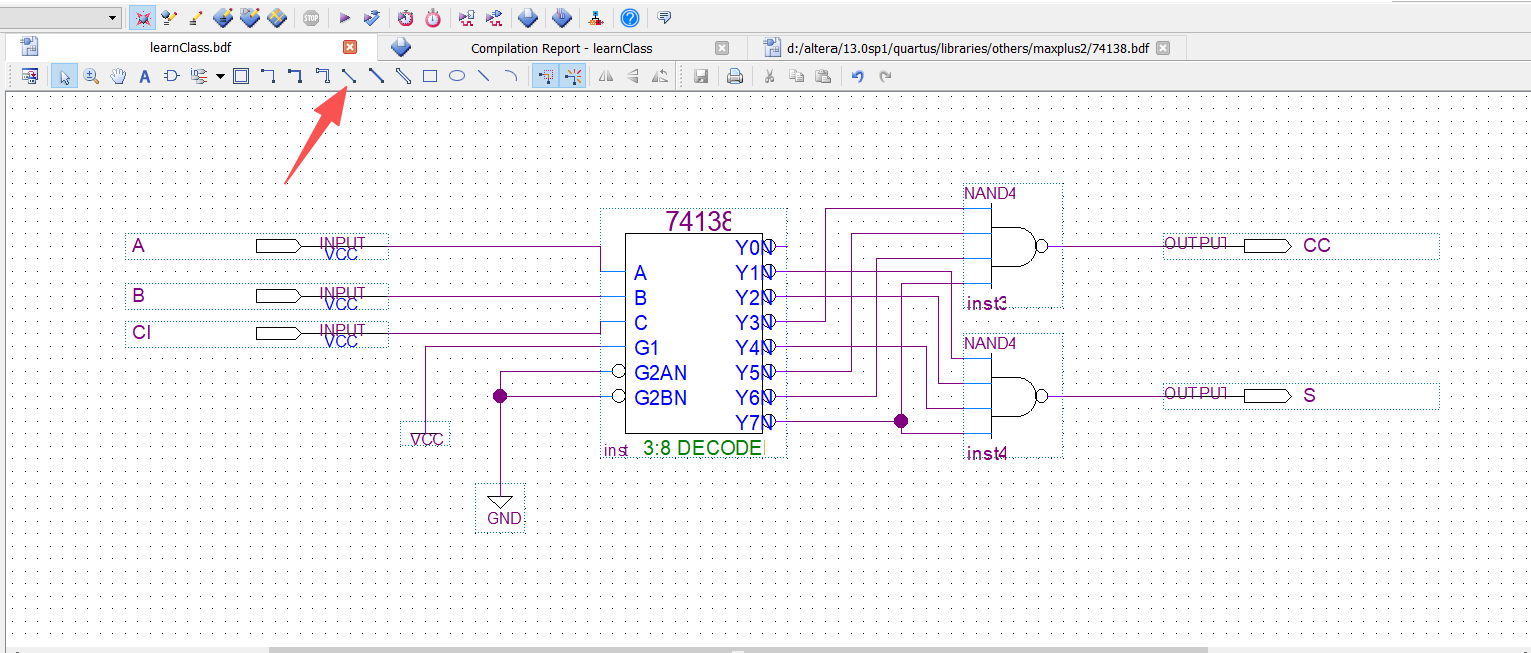

最好使用图示箭头所指的线条,按照如下接线方式连接各个组件:

注意:连接所有组件后,只允许出现图示的两个实心点,其中G2BN连接到GND----G2AN、inst4第四接线口连接到Y7N----inst3第四接线口,若出现非预期的实心点,请右键实心点将其删除

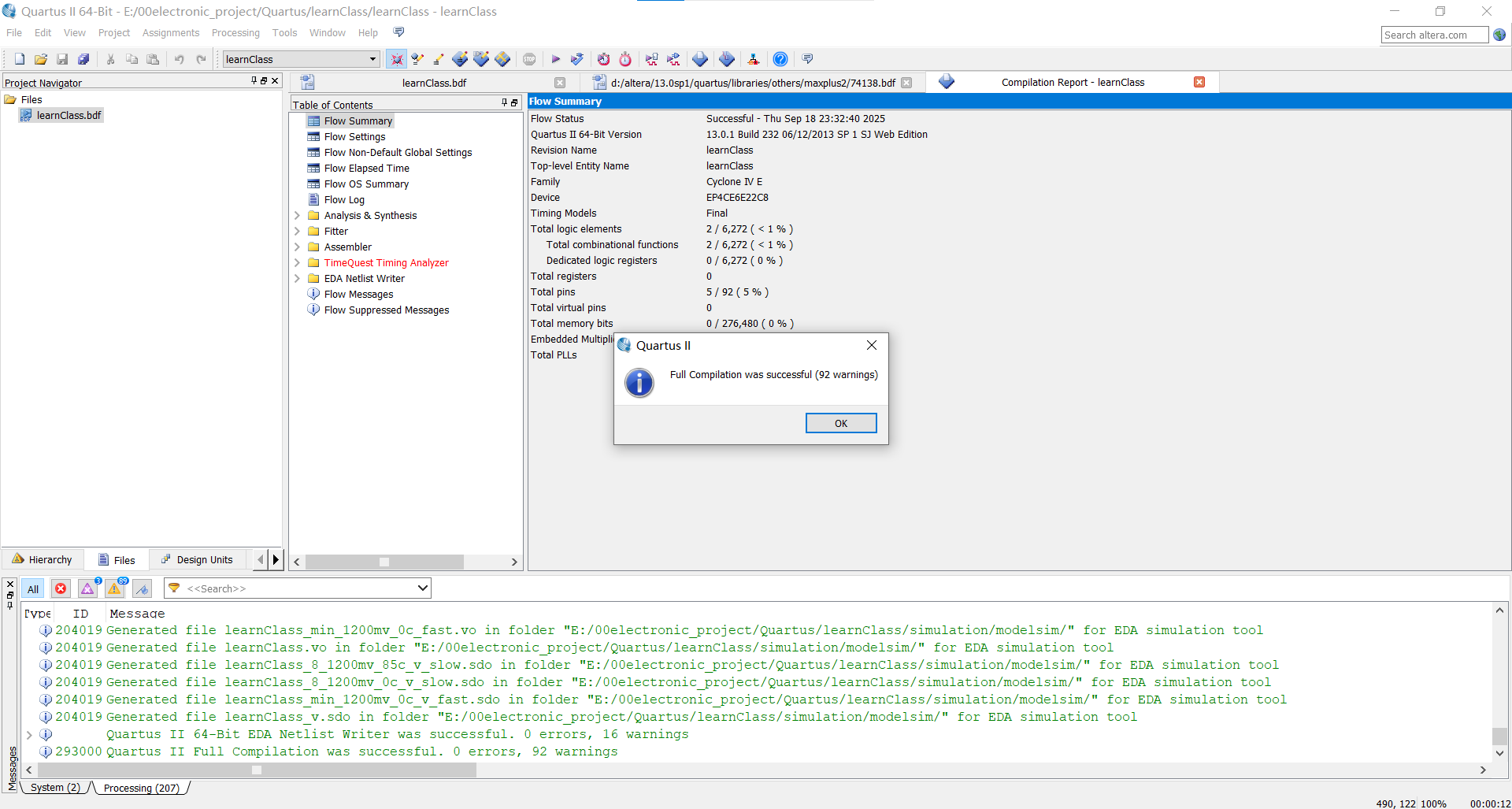

接着点击Start Compile开始编译

若未出现报错则说明绘图成功,否则请检查接线是否正确、实心点位置以及数量是否正确

4.1 模拟波形

根据 3.1 画第一个电路图 画的电路图模拟波形,观察波形变化

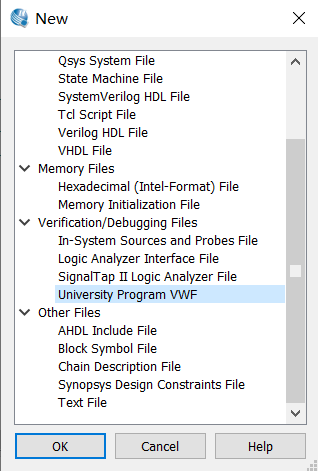

新建一个University Program VWF文件

将其另存为${project.name}.vwf文件

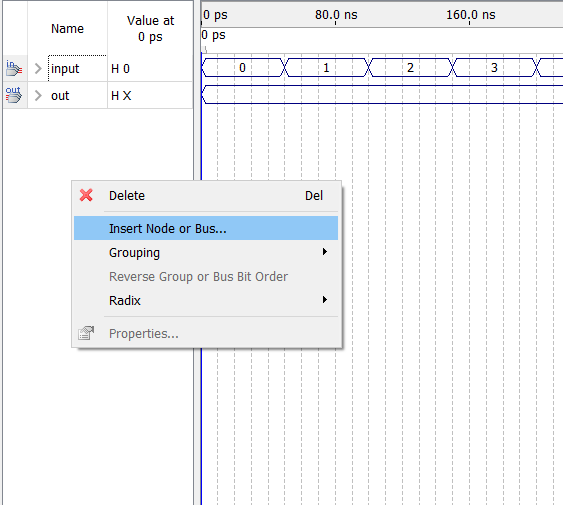

双击左侧空白处或右键点击打开Insert Node or Bus对话框

点击New Finder按钮,再点击List搜索出之前创建的所有组件,再点击 >> 选择所有搜索出的组件,

然后点击Ok,再次点击OK,接着对A、B、CI分组为input,对CO、S分组为output

再设置一下频率,然后直接点击模拟就行了

5.1 verilog代码

mux2to1:

1 | module mux2to1 (out, a, b, sel); |

mux8to1:

1 | module mux8to1 (out, a, sel,en); |